前面我們提到了buck電路的開關的振鈴波形,本質原因是LC的阻尼振盪。

文章偏理論,那BUCK到底是怎麼產生尖峰振盪呢?

要想把這個問題搞清楚,也很是不容易,所以

文章有點長,請直接點贊轉發加收藏。

問題

本期主要分析

以下這兩個問題

:

1、死區時間是什麼?這裡有個小臺階是什麼情況?

2、上下尖峰振盪是如何產生的?跟哪些因素有關?

理想的BUCK的SW波形

我們

由淺入深

,一步一步來,

先看理想的開關SW波形—沒有尖峰電壓的波形

。

為了能更好的看buck電路各個點的電壓電流情況,我選的電源晶片是沒有內部整合開關管的,使用的是

外接的MOS管,電源晶片型號為LTC7803

。

使用

LTspice進行模擬

,電路圖如下:

如果對BUCK的拓撲有了解的話,上面這個電路一眼應該就看明白了,是一個同步buck,沒有用到二極體。

這個電路的

輸入是12V,輸出是3。3V,負載等於0。5Ω,BUCK工作在連續模式

。現在我們直接看電感前面SW的波形,如下圖:

我們可以看到,這個波形很漂亮,看著就是非常好的矩形波,沒有向上的振鈴。

唯一美中不足的是,在底部有下衝

。

這是怎麼回事呢?是向下的振鈴嗎?

如果仔細觀察的話,這個

下衝的幅度大概是0。7V左右

,也沒有出現振盪波形,如此,猜測應該是二極體的導通電壓。為了驗證這個想法,我們對比兩個MOS管的驅動電壓Vgs,然後看看電感的電流。

從上圖,很容易看到,

電感的電流一直都是正的(大於0)

,也就是電感的電流總是向負載那個方向流動的,並不會反向,並且,最小的電流也有2A。

但是呢,如果我們對比兩個NMOS管的Vgs,會發現有同時為低的情況,

也就是說兩個管子同時都不導通,這一段時間就是

死區時間

。

為啥會有死區時間呢?

我們通常分析BUCK拓撲結構的時候,經常會認為只有一個管子導通,要不上管,要不下管(連續模式)。

而實際MOS管在切換導通狀態的時候,MOS管必然會存在中間態-半導導通狀態,半導通時的MOS管的導通電阻是變化的,很大到接近於0,如果兩個管子同步切換,那麼必然會出現都處於半導通狀態的情況,迴路電阻很大,這樣功率電感電流就沒法續流了。

所以呢,

必須要考慮切換時其它的續流方式

。

不僅如此,如果兩個管子同步切換,稍微有一點不同步的話,那麼肯定會存在兩個管子都導通的情況,這樣的話就相當於電源直接對地短路了,

這簡直是災難

。

現在看來,保險起見,乾脆將時間錯開,每次切換的時候,讓兩個管子都不導通一段時間,這樣就絕不會出現兩個管子同時導通了。

但是這樣的話,我們必須想辦法給功率電感續流。

這個續流的方式很容易想到,

MOS管是有體二極體的

。在兩個管子都關閉的時候,可以透過體二極體的續流。

寫到這裡,我突然想起來,有些同步的DCDC晶片推薦的電路,會有

二極體選貼一說(二極體可要可不要)

,比如這個MP1484的D1。

看到這個圖

不要以為這是一個非同步buck,二極體D1是選貼的

。

那這個二極體有什麼用呢?

其實MP1484晶片手冊裡面也有寫。

寫的很明白了:

在上管和下管轉換期間,電感電流主要從下管的體二極體流過。體二極體的導通電壓比較高,可選用一個肖特基二極體並在SW和GND之間,以此來提升整體效率。

這個器件是矽晶片,那麼顯然,體二極體也就是矽二極體,導通電壓自然要比肖特基二極體更高,因此使用肖特基二極體可以降低功耗。

不過我想這個降幅應該很是很有限的,因為上下管轉換期間的時間非常短暫,只佔開關週期很短的一部分時間,並且就算用了肖特基二極體,也還是有導通電壓,只是比之前小一點而已。

以上是模擬波形,那實際電路也會在開關切換時有個0。7V左右的“下衝”嗎?

我手頭正好有MP1484的板子,於是我用示波器測試了一下,波形如下圖:

奇怪的是,只在下降沿時出現了一個0。7V的下衝臺階,在上升沿時底部並沒有向下的“下衝”臺階。

這是為什麼呢?難道上升沿時上下管切換並沒有死區時間?

為此,我猜測可能是負載電流的太小,並且上升沿時的死區時間比較短,而MOS管的D和S是有寄生電容的。

在開關切換之前,下管是導通的,等於接地,寄生電容兩端電壓約為0V,體二極體也是0V。

在切換時,體二極體剛開始也沒有導通,所以是先對電容進行放電才能讓電壓變為-0。7V,此時二極體才會導通。如果死區時間太短,或者電感需要續的電流很小,那麼可能在死區時間結束,電容都能提供足夠的續流,電壓下降很小。

為了印證我的猜測,因為沒法加長死區時間,所以我改變了負載電阻,

加大了負載電流,目的是為了讓寄生電容提供不了足夠的續流

。

再次測試了一下,確實就能量到上升沿的死區時間了,如下圖所示

可以看到,上升沿也有一個向下的冒尖,時間非常短,拉開示波器時間尺度發現大概是13ns(就不截圖了)。而下降沿向下的冒尖時間大概是100ns。也就是說這個MP1484的兩個死區時間分別是13ns和100ns。

從前面的模擬波形可以看到,在開關管切換時,死區時間會導致SW處出現0。7V左右的負壓臺階,但是完全看不到尖峰。

而實測波形是有尖峰的,那這個尖峰是如何產生的呢?它的大小與哪些因素有關係呢?

我們接著看。

當然,我上圖中實測的尖峰也很小,這是因為我做的板子已經儘量最佳化PCB了,所以尖峰效果不明顯,如果板子做得差的話,可能是下面這樣的。

拉開可以看到是

高頻振盪

我們知道,這個

尖峰過高

,意味著存在高頻的劇烈變化的電流,會產生

EMI的問題

,同時,如果太高的話,可能會擊穿內部開關管。

如果我們想要降低尖峰,最好的方式

莫過於知道這個尖峰是如何產生的

,然後對症下藥。

BUCK的SW波形尖峰如何產生

首先一個問題,模擬沒有出現尖峰,是什麼原因呢?

是因為器件模型不準確嗎?也許吧,模擬使用到了整合晶片,NMOS管,電感和電容,那麼如何確認這個問題呢?

更新功率電感模型

功率電感FCUL1060-H-R56M我使用的是LTspice庫裡面自帶的。

裡面的寄生引數很少,我只看到了Rser,寄生電容都看不到,因此

我有理由懷疑這個模型不準確

。

既然有懷疑,那就單獨測試下這個電感的阻抗曲線。測試方法很簡單,用1A的電流源,採用AC頻率掃描的方式,測量電感兩端電壓就可以了。

因為電流是1A,所以阻抗值與測得的電壓相等,測試電路與結果如下圖:

實線是阻抗,虛線是相位。

很顯然,這個

電感模型有問題

,或者說是不夠準確吧,因為阻抗隨頻率的增大而增大,

連自諧振頻率都看不見

。

因此,我從村田下載了FCUL1060-H-R56M的Spice檔案,重新構建模型,再次測試阻抗曲線如下圖:

注意,上圖中

U1就是重新生成的電感模型

,這個LTspice軟體開啟spice檔案,然後自動建立的電感模型,所以在LTspice看來,它是一個模組,位號就成了U1,大家知道這是我生成的電感模型就好。

可以看到

自諧振頻率大概是100Mhz

,這個模型應該是比較準確的,看起來是那麼回事。

其實我們也可以從spice檔案提取出這個電感的等效電路模型,spice檔案本質來說就是個網表

上圖是我根據spice檔案畫出的等效電路模型,模擬一下會發現阻抗曲線與前面的一模一樣。可以看到,這個官網提供的電感的spice檔案還是挺複雜的,它建立的電感的模型應是更為準確的。

我們平時可能會說電感的高頻模型是下圖這樣的。這也不能說錯,只能說不夠準確,因為我們平時也不需要那麼精確,因此下圖也就夠用了。

而這次我們需要更精準的模型,所以用廠家官網提供的spice檔案是最好的。

更新電容模型

同樣的方法,我從官網下載我使用的22uF和100uF電容的spice檔案,構成新的模型,測試阻抗曲線如下圖所示

同樣,實線是阻抗,虛線是相位

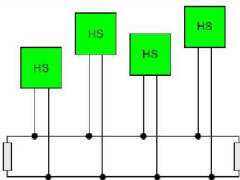

使用新的電感和電容模型,放入到原來的電路中,電路如下所示:

電感和濾波電容均使用了從官網下載的spice檔案構建的模型,模擬SW的波形如下圖:

與更新模型之前相比,基本沒差別

,這說明問題不在更新的模型上面。

LTC7803只是一個驅動晶片,產生Vgs訊號,用作驅動MOS管開關,拋開開關速度不談的話,應該跟尖峰關係不大。那就只剩下MOS管的原因了。

我們接著看

更新MOS管模型

從前面知道,LTspice軟體自帶的模型很可能是簡易的,也就是說是不夠精確的,NMOS管很有可能也是如此。

電路圖中MOS管使用的是BSC059N04LS6,廠家是Infineon,我從官網上面下載spice檔案,根據spice構建新的模型,換到前面的電路中,電路更新如下圖:

模擬SW波形如下圖:

久違的振盪尖峰終於出現了。。。有一絲興奮。。。

上下尖峰幅度差不多,大概有8V。

現在已經看到了類似於我們現實中的尖峰,那麼問題來了,

這個尖峰到底是怎麼產生的呢?

目前看到的就是我們換了一個MOS管的模型就出現了。

這個官網提供的MOS管模型到底有什麼不同呢?

上圖是官網下載的MOS管的spice檔案,需要特別注意的是有三個引數,

Lg,Ld,Ls這是3個電感分量

。

它的意思是,在MOS管的G,D,S極上面分別串聯了電感。

因此,我猜測就是因為引入了這3個電感分量,所以才有了振盪尖峰。

之所以有此猜測,是因為振盪尖峰產生的原因一般就是因為LC阻尼振盪,MOS管的模型一般都不會少了電容,而電感卻不一定有。

為了驗證到底是不是這三個電感的原因,我將Lg,Ld,Ls都改成了1fH,1fH等於10的負六次方納亨。其實我是想改為0的,只不過改為0後模擬出現不收斂的情況,因此就改成了1fh,這也足夠小了。

將電感引數改為1fH。

建立一個新的模型,替換到電路中,再次模擬一下。

會看到SW的尖峰沒有了,所以可以肯定的是,

MOS管上面串聯的電感是產生尖峰的必要條件

。

那問題又來了?能不能直接從拓撲結構分析下,電感是產生尖峰的必要條件?

先來看產生尖峰的時候,兩個開關管的開通與關閉情況。以

上升尖峰

為例。

紅色的波形是上管的Vgs電壓,藍色的是下管的Vgs電壓,綠色的為SW電壓,最下面的為電感電流。

MOS管使用的是BSC059N04LS6,我們檢視晶片手冊,會發現在Vgs的開啟門限最大是2。3V。而在在SW處產生尖峰振盪的時候,Vgs都在3。5V以上,也就是說上管已經完全導通了,而此時下管是完全關閉的,這可以從上圖中的波形中看出來。

也就是說,

上尖峰振盪的時候,上管完全導通,下管完全關閉

,不是在開關開始切換,半導體的時間段。

上管完全導通說明什麼呢?

儘管上管有寄生電容,但是此時上管完全導通,導通電阻只有幾毫歐,所以這個寄生電容也被短路了。

如果沒有串聯的寄生電感存在,那麼就相當於是輸入電源直接通過幾毫歐的電阻接到了SW管腳,而輸入電源電壓可以認為是基本不變的。

所以沒有電感的話,SW處不可能產生高達8V的尖峰振盪。

只有中間存在寄生電感,才會因為電流變化非常快,足以在電感上面產生8V的電壓

。

那具體過程是怎麼樣呢?

在上管導通之前,功率電感從下管的體二極體續流,下管的寄生電容C2電壓為0。

在上管導通之後,其導通電阻只有幾毫歐,因此C1相當於被短路。下管完全斷開,但是上面有寄生電容C2。

我們看SW節點,因為我們現在分析的是很小的一段時間,

所以功率電感此時可以看作恆流

,電流方向流向負載。

可能有人會認為功率電感也有寄生電容引數,能走高頻電流,所以不能看作恆流源

。關於這一點,其實我也懷疑過,這也是我要更新模型的原因。

不過檢視功率電感的電流波形,在振盪時間段,確實是基本不變的。

另外我們知道,振盪頻率是百兆量級的,而我們檢視這個功率電感的阻抗曲線,其自諧振頻率就在100Mhz左右,此時阻抗最大,阻抗達到了上千歐姆,所以它是無法透過高頻的電流的。

我們繼續。

我們知道,

SW節點處穩定之後基本等於電源電壓

。

在開關導通之後,SW從0V電壓開始上升,那麼C2在被充電,電源需要透過L1提供功率電感L3的續流以及對C2的充電。

也就是說:L1的電流=功率電感L3的電流+C2的充電電流

隨著SW節點的電壓升高,一直到SW電壓和Vin一樣,這時候電壓為什麼不停止上升呢,直接達到穩態呢?

這是因為

L1的電流=功率電感L3的電流+C2的充電電流

,也就是說在SW電壓達到Vin之前,L1的電流>功率電感電流。

在SW電壓達到Vin時,如果電壓不再上升,那麼意味著C2不再被充電,即流過C2的 電流為0,那麼L1的電流=功率電感電流。

而事實是L1的電流>功率電感電流。

所以在SW達到Vin電壓之後,SW電壓繼續上升,會大於Vin,此時電感L1兩端的電壓反向,電流開始減小。

隨著SW電壓上升,那麼C2繼續被充電。當L1的電流減小到和功率電感一樣的時候,因為

L1的電流=功率電感L3的電流+C2的充電電流

。那麼意味著C2的充電電流為0,就不能透過L1接著對C2進行充電了。

此時SW電壓達到最高,但它也不能保持住,為啥呢?

因為此時SW的電壓大於Vin,電感L1的電流要繼續減小。而功率電感L3的電流不變,所以功率電感必須從C2抽取電流,這意味著C2開始放電。

C2開始放電後,SW電壓開始降低,然後SW的電壓降低到Vin,此時L1的電流達到最小。再之後C2繼續放電(因為L1電流小,不足以提供功率電感的續流),SW電壓繼續降低,L1兩端電壓反向,L1的電流開始增大,直到L1電流大小達到功率電感的電流。

此時C2停止放電,SW電壓達到最低,然後C2開始被充電,SW電壓開始升高,如此迴圈往復,SW處電壓看起來就是振盪了。

當然整個過程中因為有電阻分量,所以振盪幅值是越來越小的,本質就是LCR阻尼振盪。

簡易的等效電路如下:

濾波電容的寄生電感,電阻,還有迴路中的走線電感,電阻,都是處於振盪迴路。

上管到輸入濾波電容之間的電感量對上升沿尖峰的大小起了決定性的作用

,因為尖峰的大小基本就等於L1的兩端電壓(忽略Ron兩端的電壓)。如果沒有L1的存在,振盪雖然還存在,但是SW處的電壓基本是不變的,就越等於Vin。

很明顯,如果

寄生電感L1比較大,那麼產生的尖峰電壓肯定是越大的

。

那負載電流大小與振盪尖峰的大小有關係嗎?

關係是有的,負載電流越大,那麼意味著功率電感電流越大,在SW從0上升到Vin電壓時,寄生電感L1得到的電流也越大,L1獲得的用於振盪的能量也是越大的。用於振盪的能量越大,那麼振盪尖峰自然也就越高。也就是說

負載電流越大,參與振盪的能量越多,那麼產生的尖峰也是越高的

。

同樣的,

開關速度越快

,寄生電感電流上升的速度也越快,在SW從0上升到Vin電壓時,寄生電感L1得到的電流也越大,參與振盪的能量也越多,

所以尖峰也越高

。

以上就是上尖峰的分析過程如果從文字描述的過程看,相當的複雜,下尖峰也就不分析了,疲了。。。。

我們來看點輕鬆的,直接看實驗過程。

如何看寄生電感的影響有多大呢?

前面我們不是將Lg,Ld,Ls三個引數改成接近於0的值,重新構建模型,尖峰就消失了麼?我們繼續使用該模型,然後

手動在電路上面串聯電感,然後修改不同的電感值,看看尖峰的大小

。

1、只在上管串聯0。5nH電感,下管沒有串聯電感,負載為0。5Ω,電壓為3。3V,那麼負載電流為6。6A。

可以看到此時上尖峰最高為4V,而下尖峰是沒有的(負的電平為死區時間的0。7V體二極體壓降)。

這說明上尖峰的大小是由上管的寄生電感決定的,下尖峰的大小是由下管的寄生電感決定的。

2、將上管串聯0。5nH電感改為0。8nH

可以看到上尖峰最高為8V,比原來4V高了不少,這說明

電感越大,尖峰越大

3、我們順便還可以改變一下負載,看一下電流對尖峰的影響。

保持上管串聯0。8nH,負載電阻減小一倍,即負載電流增加1倍,為13。2A。

可以看到,上尖峰達到了19V,增大了很多。這說明了

負載電流越大,尖峰越大

。

這跟前面分析是一致的,負載電流越大,上下管切換的時候,寄生電感獲得的參與振盪的能量越高,尖峰也越大。

4、我們去掉上管的串聯電感,下管串聯0。8nH,負載電流還是13。2A

電路圖如下圖:

模擬的SW波形如下圖:

可以看到,沒有上尖峰,下尖峰大概有10。5V,這說明了

下尖峰的大小是由下管的寄生電感決定的

。

5、我們給上管和下管都加上0。8nH的電感,負載電流還是為13。2A

電路圖如下:

模擬的SW波形如下圖:

這時,可以看到,上下尖峰同時存在。上尖峰是14V左右,下尖峰是10V左右。

這裡又存在一個問題了。。。為什麼電感都是0。8nH,下尖峰的值更小?

我同時檢視Vgs與SW波形,發現,上尖峰振盪發生在

上管導通,下管不導通

的時間段

而下尖峰發生在

死區時間,上下管子都不導通

死區時間,意味著功率電感的續流是透過下管的體二極體,我們知道體二極體有壓降,會損失能量。所以說

下尖峰比上尖峰多了一個體二極體的損失能量,所以尖峰更小

。

寄生電感相同時,那麼下管尖峰一定比上管小嗎?

我們接著看

6、上管和下管都加0。8nH電感,負載電阻增大到0。5Ω,負載電流減小一半,為6。6A

可以看到,電流改小之後,上下尖峰都減小了,這也與前面的分析一致。不過現在上下尖峰都是7V左右,二者差不多,

並沒有像前面說的下尖峰更小,這又是為什麼呢?

我們再開啟功率電感電流和Vgs的波形

上升沿尖峰時,功率電感電流是最小的

,功率電感續流需要走上管,也就是說最終上管的0。8nH所需要的達到的電流較小,這會導致尖峰比較小。

而下尖峰時,功率電感電流是最大的

,功率電感續流需要走下管,也就是說最終下管的0。8nH所需要的達到的電流較大。這會導致尖峰比較大。

所以,上下尖峰的大小誰大誰小,視情況而定

。

我們極端一點,如果這個buck工作在斷續模式,那麼意味著上管導通時,功率電感電流是0,也就是說功率電感需要透過上管續的電流為0,

那豈不是上尖峰應該消失呢?

我們來看一下。

7、將負載電阻改為1Ω,負載電流為3A,buck進入斷續模式,我們來看看上尖峰是否為0

SW波形如下:

可以看到,上升沿尖峰並沒有消失,

好像與前面的分析不符啊,什麼情況呢?

我們看一下上管0。8nH的電感電流,功率電感電流在上升沿時的情況。

可以看到,在上升沿時,功率電感的電流確實為0,但是上升尖峰還是存在,因為0。8nH的電感是有電流存在的。

那這是為什麼呢?

這是因為的MOS管的DS的兩端有寄生電容Coss,在上升沿之前,下管導通,Coss的電壓為0V,而導通之後,最終Coss的電壓是為12V的,這期間就構成了LC的振盪電路。

除了以上這些,尖峰的大小還與哪些因素有關係呢?

很容易想到的就是MOS管的開關速度,這個我們可以在柵極加電阻,來增加導通時間。導通時間增加,在開關管切換的時候,

8、開關速度對尖峰大小的影響

在上下管串聯0。8nh電感,負載電流為13。2A,MOS管柵極沒有串聯電阻時。

MOS導通時間大概是7ns左右,上尖峰高度為14V

我們在上管柵極新增10歐姆電阻,電路如下

執行,Vgs的電壓與SW波形如下圖。

可以看到,上MOS管柵極加了10歐姆電阻之後,從截止到導通的時間大概是13ns,比原來7ns時間更長,另外,SW的尖峰幅度也從14V降低了到9V。

總的來說

,BUCK上下尖峰的產生,與線路中的電感是密不可分的,電感越大,尖峰也就會越大。如果上下管沒有電感的存在,是產生了尖峰的。

除此之外,還與開關管的開通速度也有很大的關係,開通越快,產生的振鈴尖峰也越高。

這個我估計有人就說了,

你廢了半天牛勁,整出一堆沒用的

。

我們一般用的BUCK晶片都是整合的,內部集成了MOS管,我們線上路上面也不會額外加電感,

有什麼用呢?

實際電路中的電感是如何存在的?

前面做的一系列實驗,那個0。5nH/0。8nH電感,可以看作是

線路中的寄生電感。

實際電路很複雜,晶片內部引線電感,PCB走線電感,濾波電容的等效ESL等等。

當然,晶片內部我們沒法改變,我們能改變的就是輸入濾波電容的位置,晶片好好接地。透過

最佳化PCB Layout降低走線電感量

。

可能有人就說了,

走線電感,聽著這麼玄乎,真的有這麼大的影響嗎?

確實是真的。我上面模擬電路放的電感最大也才0。8nH,可以看到,引起的尖峰已經很大了。

而0。8nH的電感量什麼概念呢?到底大不大?

如圖所以,1盎司銅厚,線寬50mil,走線長度10mm的電感量是6。52nH。可能我們輸入濾波電容會放得很近,但是一般距離也有個2mm左右吧,這樣走線電感也差不多1nH。

所以呢,在研究

振盪尖峰這個問題時,走線電感是不能忽略的

。

而事實確實也是如此,我們用示波器測量實際電路的時候,都是會量到這個振盪尖峰的,只不過有大有小而已。

在設計中,選定了BUCK晶片之後,我們能做的其實不多。

就是

儘可能的將輸入濾波電容放得離晶片更近,巴不得直接將輸入濾波電容跨接在晶片的輸入管腳和地管腳上面,這樣輸入環路最小

。

這一點也應該是

PCB layout裡面最重要的一點

吧。

有的DCDC晶片的管腳分佈並不好,

PCB layout時可能需要將輸入濾波電容放到PCB板背面去

,這個時候就需要特別注意了,

過孔一定要儘可能多打幾個

。

為啥要多打過孔呢?

自然是因為過孔的寄生電感也是不能忽略的。

從上圖可以知道,

10/20mil的過孔的寄生電感達到了1nH

,這電感量也是不小的。

所以我們在PCB layout的時候,如果是電容放置在背面,一定要多打些過孔,因為電感並聯,總電感量是減小的。

多打過孔並不僅僅是考慮過流能力

在過流能力夠的情況下,如果一個老工程師要求你打幾個孔,或者把孔徑加大。或許你認為是在為難你,也許是別人站的高度更高。

小結

文章有點長,做了大量的模擬與分析,主要結論如下:

1、死區時間是同步buck中必然存在的,如果用示波器測到在開關切換時,有個負壓的臺階,請不要驚慌,那是正常現象

2、寄生電感是BUCK上下沿振盪尖峰存在的必要條件。在做電路設計時一定要注意減小寄生電感。

3、開關速度越快,寄生電感越大,那麼振盪尖峰也會越大。

4、振盪尖峰與PCB Layout的關係非常大。

資料下載

1、文件

關於振盪尖峰的,我有看到一個非常好的資料,大家也可以看一看。裡面有說如何加RC緩衝電路(Snubber電路),如何在自舉電路上面串聯電阻降低開關速度等,也做了較多實驗。

檔案是在Richtek網站上下載的,檔名是《

消除 Buck 轉換器中的 EMI 問題

》

2、我用LTspice模擬檔案:包括原理圖,spice檔案,自建的模型庫,大家有需要自提

。

需要注意

,拿到我模擬檔案直接執行可能不行,需要新增庫的路徑,修改下自薦模型的屬性。

下載方法

在我的

微信公眾號“硬體工程師煉成之路”後臺

回覆“

煉成之路

”,即可獲得下載連結。

公眾號相關留言